project overview

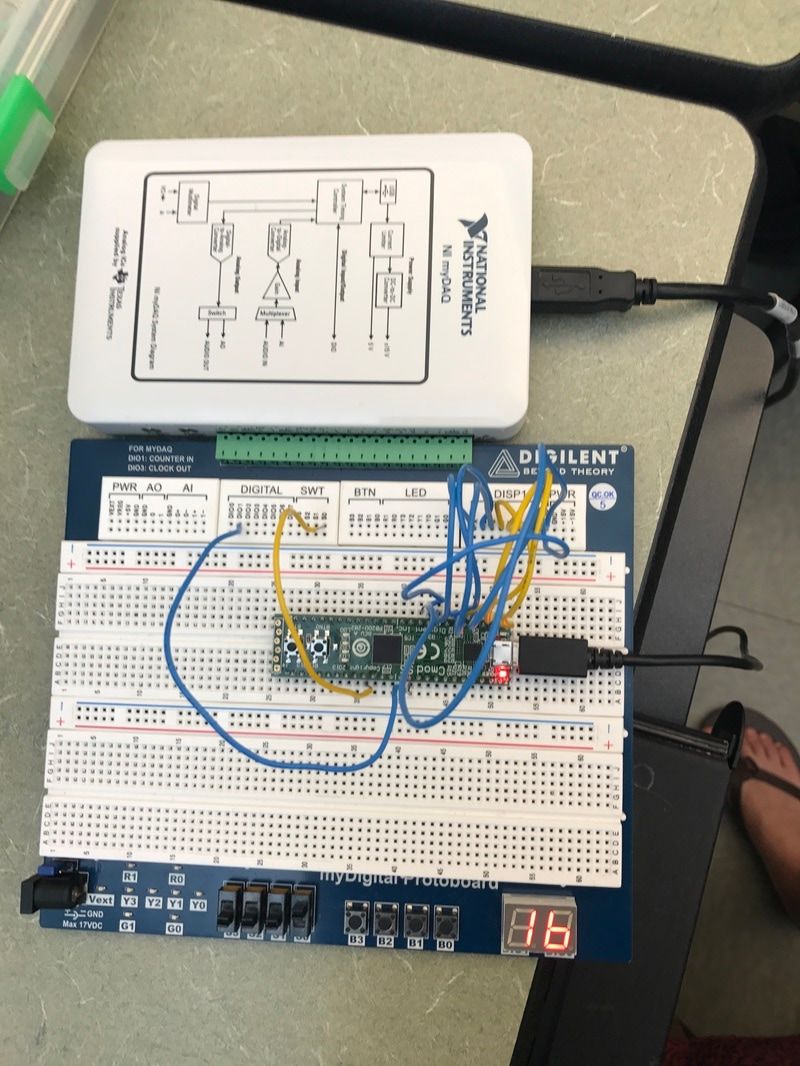

In this project, we were tasked to design a counter that counts from 0-60 seconds. We used J/K flip flops for the tens column and a 74LS163 MSI counter for the ones column. There is also a reset signal. When the counter detects a six in the tens column and a zero in the ones column (60), the counter will reset to zero in both columns. This counter is synchronous, meaning that all of the segments are clocked by an external clock.

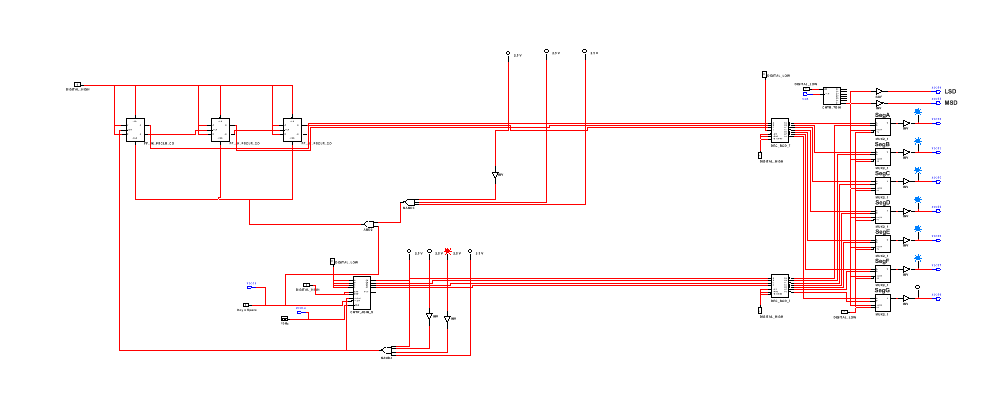

pld circuit

conclusions

Synchronous counters consist of segments that are each clocked by an external clock. On the other hand, asynchronous counters consist of segments where the first segment is clocked by an external clock. All subsequent flip-flops are clocked by the output of the preceding flip-flop. This is also known as a ripple effect. Synchronous counters are faster than asynchronous counters and no do suffer from the ripple effect. However, they do require more logic. There are many differences between the '163 and '193. The '163 consists of a synchronous load and clear. It can only count up and it must start at zero. The '163 is also different from the '193 because the detected number is what you see last. What you see is what you get. For the '193, it can count up or down and it does not have to start at zero. It is an asynchronous load and clear. The '193 will not detect the last number. The circuits of my classmates were pretty much similar to mine. They were a little different in some ways, like having one less AND gate or one more NAND gate, etc.

The sixty second counter was very similar to the 0-80 counter. It used J/K flip flops and the 74LS163 MSI counter instead. In order to construct this circuit, first, you must connect all of the necessary inputs to their outputs. For the tens column, the J's, K',s and presets all must be connect to power. The clears must all be connected to themselves. Since it is counting up, Q' must be connect to the clock on the next flip flops. The Q' of the last flip flop will not be connected to anything. Finally, you must connect A-C on the DEC to Q on each flip flop. The D is connect to a digital low and the rest are connect to digital high. For the ones column, you will use the '163 MSI counter. Segments B and C will have inverters while A and D will not. In order to connect these two circuits, you will use one NAND gate and one AND gate. You will connect the NAND gate to the Q's of the J/K flip flops. The output of the NAND gate will be connect to an AND gate. The other input to the AND gate will be connected to the switch. The output of the AND gate will be connected to the clear of the J/K flip flops of the tens column. The 74LS163 MSI counters (of each the ones and the tens column) will be connected to the circuit that Ms. Zienty supplied. This will create the sixty second timer.

The sixty second counter was very similar to the 0-80 counter. It used J/K flip flops and the 74LS163 MSI counter instead. In order to construct this circuit, first, you must connect all of the necessary inputs to their outputs. For the tens column, the J's, K',s and presets all must be connect to power. The clears must all be connected to themselves. Since it is counting up, Q' must be connect to the clock on the next flip flops. The Q' of the last flip flop will not be connected to anything. Finally, you must connect A-C on the DEC to Q on each flip flop. The D is connect to a digital low and the rest are connect to digital high. For the ones column, you will use the '163 MSI counter. Segments B and C will have inverters while A and D will not. In order to connect these two circuits, you will use one NAND gate and one AND gate. You will connect the NAND gate to the Q's of the J/K flip flops. The output of the NAND gate will be connect to an AND gate. The other input to the AND gate will be connected to the switch. The output of the AND gate will be connected to the clear of the J/K flip flops of the tens column. The 74LS163 MSI counters (of each the ones and the tens column) will be connected to the circuit that Ms. Zienty supplied. This will create the sixty second timer.